### 2 第4世代光電融合技術

## 通信とコンピューティングを結ぶ 光電融合デバイスの実現に向けて

IOWN 構想の基盤である光電融合技術に取り組んでいる。通信速度が向上するにつれて光が導入される伝送距離はますます短くなっている。われわれの取り組む第4世代では伝送距離が数 m のコンピューティングへの導入を目指している。接続する相手は Ethemet スイッチ LSI から CPU などの計算用 LSI 間になり、小型化・低消費電力化・プロトコル対応の課題に取り組む。

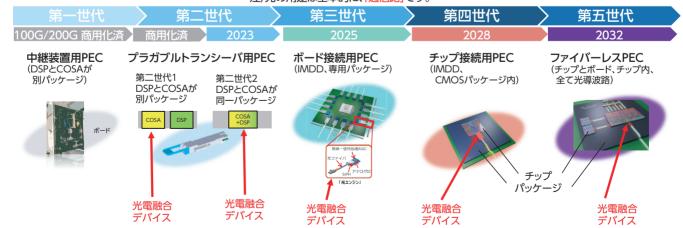

#### NTT における光電融合技術の ロードマップ

NTT デバイスイノベーションセンタでは、IOWN 構想を支える光電融合デバイス技術の開発を進めている。光電融合技術のロードマップが図1である。それに沿った開発を進めており、2023年8月の組織整備に伴い、第一~三世代はNTTイノベーティブデバイス株式会社にて開発・製品化を進め、第四世代はNTT先端集積デバイス研究所での研究からデバイスイノベーションをフタでの開発へミッション移行され

た。光は数 100kmの 長距離から 2km以下 のデータセンタ内ま で、電気配線の不得ま で部分を置き換える。 ・電気を用いた伝 は、LSI からみた場合 に LSI パッケージから ボード上、ボードから ボード上、ボートから ボルまで使われてい

る。今後、伝送速度の高速化に伴い、 これらの部分の距離が長いところか

NTT デバイスイノベーションセンタ 光インターコネクトデバイスプロジェクト 光送受信サブシステムグループ (左) グループリーダ 佐藤 昇男 氏 光送受信ナノデバイスグループ (右) グループリーダ 瀬川 徹 氏

ら光が導入されていくトレンドを予 想している。

#### ネットワークからコンピューティングへ 注)光の用途は基本的に、通信路です。

図 1 光電融合技術のロードマップ (PEC: Photonics-Electronics Convergence, DSP: Digital Signal Processor, COSA: Coherent Optical Sub-Assembly)

特に、第一~三世代までは通信用 途が強く、長距離・インターネット・ LAN 用 の Optical Transport Network (OTN) 規格や Ethernet 規格に準拠している。一方で第四世 代以降は距離が短く、接続先が CPU や GPU などの演算用 LSI と なり、通信からコンピューティング への用途にシフトしていく。CPU のインタフェース規格はメモリに加 え、Peripheral Component Interconnect express (PCIe) が標 準として普及している。このように 第四世代では規格が異なるととも に、適用先も通信装置から計算用 サーバに変わる。

#### コンピューティングに 光を導入するメリット

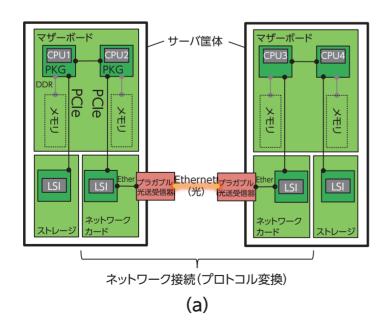

コンピューティングに光を導入するメリットについてサーバ構成を例に説明する(図 2)。AI では多くの計算リソースが必要になり、複数のプロセッサコアや CPU を使う場合がある。従来のサーバ構成例(a)

では、マザーボード上にある2個 の CPU (CPU1-CPU2) 間の接続 は容易だが、異なるマザーボード/ サーバ筐体にある CPU (CPU2-CPU3) 間の接続はネットワーク接 続とプロトコル変換が必要となる。 すなわち、ネットワークカード上の プロトコル変換用の LSI で PCIe か ら Ethernet に変換し、Ethernet 対 応のプラガブル光送受信器で接続 し、隣のサーバ筐体の中で逆の変換 をしている。このため、消費電力と 遅延が大きいという問題がある。一 方、光電融合デバイスを用いたサー バ構成イメージ(b)では、異なる マザーボード間の CPU (CPU2-CPU3) でもプロトコル変換をする ことなく直接接続することができ る。また、電気に比べて距離を長く とれるため、ストレージなどを複数 備えたリソースプールを構成でき る。これにより、従来例(a)ではサー バ筐体単位(図の黒線枠)での接続 だったものが、提案構成例(b)で はパッケージ (PKG) に入った CPU単位の細かい粒度で接続することができる。CPUの直接接続では消費電力や遅延を低減できるだけでなく、時間変動するワークロードに応じて必要な計算リソースだけを選択して接続できる。これにより、不要なリソースを待機させて無駄を省き、電力効率を向上させることができる。図ではサーバ2台の例を示したが複数台からなるファブリックへの拡張性も高い。

このようなサーバ構成の考え方は、コンポーザブルサーバ(構成が可能なサーバ)やディスアグリゲーテッドコンピューティング(細かく分解されたコンピューティング)と呼ばれて、実現に向けた開発が各社にて進められ商用機も提案がされている。NTTでもIOWN構想における「スーパーホワイトボックス」が該当し、この要素技術が第4世代光電融合デバイスである。

このような形態を実現するためには、光電融合デバイスが CPU を含む LSI パッケージ内(数 cm 角)に

図 2 (a) 従来のサーバ構成例

(b) 光電融合デバイスを用いたサーバ構成例

入るほど、小型化される必要がある。 それを可能にする一番のコア技術となる光デバイスについて次に説明する。

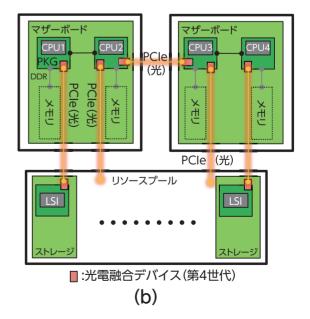

#### コアとなる光半導体技術の 実用化に向けて

光デバイスをLSIパッケージ内に格納するためには、小型化とともに低消費電力化と低コスト化が重要である。低消費電力化のためには、小さな電力で高速に光デバイスを変調することが重要である。低コスト化に向けては、複数の送受信素子を光フィルタ回路などの機能素子を一体集積し実装コストを削減することが望ましい。この際、Si-LSIで用いられる微細加工技術を利用して高性能な光回路を作製するSiフォトニクス技術を利用することが重要となる。

図3に第4世代光電融合のコア技術として進めているメンブレン光デバイスと従来の化合物半導体光デバイスの断面構造図を示す。メンブレン光デバイスは図に示すように 0.3 ミクロン程度の薄い活性層が低屈折率な SiO2 膜の上に集積されている。このため活性層への光閉じ込めが強いのが特徴である。一方、従来構造では、活性層の上下を同程度の屈折率を持つ InP 層で挟んだ厚さ数ミ

クロン程度の構造となるため光閉じ 込めは提案構造と比較すると 1/3 程 度と小さくなる。

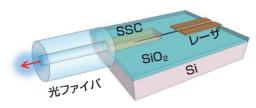

提案するメンブレン光デバイス は、活性層への光閉じ込めが強いこ とから、高い変調効率をもつ直接変 調レーザや光変調器が作製可能とな る。また、スポットサイズ変換器 (spot size converter: SSC) を集積 可能であることから光ファイバアレ イ等との結合も容易になる(図 3-b)。さらに、Si 光回路上に集積 できるため、Si導波路で作製した 光フィルタ回路と集積して波長多重 技術を適用することも可能である。 したがって、高密度に低電力な光デ バイスを集積化することが求められ る LSI パッケージ内の光インター コネクションのキーデバイスとして 期待される。

約 1Tbps/2mm = 約 0.5Tbps/mm 以上の帯域密度をもつ光チップレットが必要となる。この帯域密度は、 現在普及している光トランシーバと 比較して 100 倍以上の値である。 この光チップレットと計算用 LSI とを同一パッケージ基板上に実装す ることで計算用 LSI は光のインタ フェースを備えることになり、LSI 単位での計算リソースの効率的な利 用ができる。

今後、光チップレットを実現する ために必要な高密度かつ低電力なメ ンブレン光デバイスとそれを駆動す る電子回路、それらを集積するため のパッケージ技術や光・電気実装技 術の確立を進め、将来の情報処理基 盤の発展に寄与する。

#### 今後について

今後は、LSI パッケージに入るほど小型で大容量、かつ低消費電力な光トランシーバ、いわゆる光チップレットの実現をめざす。例えば、PCIe6 では、16 レーン構成で64 Gbps/レーン、合計 1.024Tbps となるため、この送受信機能を例えば約 2mm 幅におさめようとすると、

# 提案の構造 従来の構造 P-InP ~3μm SiO2 活性層 n-InP n-InP 板

(a) 提案構造と従来構造の比較

図3 メンブレン光デバイスの構造

(b) Si 基板上のメンブレンレーザ